# Solution-Processable LaZrO<sub>x</sub>/SiO<sub>2</sub> Gate Dielectric at Low Temperature of 180 °C for High-Performance Metal Oxide Field-**Effect Transistors**

So Yeon Je,<sup>†</sup> Byeong-Geun Son,<sup>†</sup> Hyun-Gwan Kim,<sup>‡</sup> Man-Young Park,<sup>‡</sup> Lee-Mi Do,<sup>§</sup> Rino Choi,<sup>†</sup> and Jae Kyeong Jeong\*,<sup>†</sup>

<sup>†</sup>Department of Materials Science and Engineering, Inha University, Incheon 402-751, Korea

<sup>‡</sup>Research Center for Nano-Materials, DNF Co. Ltd., Daejeon 306-802, Korea

<sup>§</sup>IT Convergence Technology Research Department , Electronics and Telecommunications Research Institute, Daejeon 305-700, Korea

Supporting Information

ABSTRACT: Although solution-processable high-k inorganic dielectrics have been implemented as a gate insulator for highperformance, low-cost transition metal oxide field-effect transistors (FETs), the high-temperature annealing (>300 °C) required to achieve acceptable insulating properties still limits the facile realization of flexible electronics. This study reports that the addition of a 2-dimetylamino-1-propanol (DMAPO) catalyst to a perhydropolysilazane (PHPS) solution enables a significant reduction of the curing temperature for the resulting SiO<sub>2</sub> dielectrics to as low as 180 °C. The hydrolysis and condensation of the as-spun PHPS film under humidity conditions were enhanced greatly by the presence of DMAPO, even at extremely low curing temperatures, which allowed a smooth surface (roughness of 0.31 nm) and acceptable leakage characteristics  $(1.8 \times 10^{-6} \text{ A/cm}^2)$ at an electric field of 1MV/cm) of the resulting SiO<sub>2</sub> dielectric films. Although the resulting indium zinc oxide (IZO) FETs exhibited an apparent high mobility of 261.6 cm<sup>2</sup>/( $\overline{V}$  s), they suffered from a low on/off current ( $I_{ON/OFF}$ ) ratio and large hysteresis due to the hygroscopic property of silazane-derived SiO<sub>2</sub> film. The I<sub>ON/OFF</sub> value and hysteresis instability of IZO FETs was improved by capping the high-k LaZrO<sub>x</sub> dielectric on a solution-processed SiO<sub>2</sub> film via sol-gel processing at a low temperature of 180 °C while maintaining a high mobility of 24.8 cm<sup>2</sup>/(V s). This superior performance of the IZO FETs with a spin-coated LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer gate insulator can be attributed to the efficient intercalation of the 5s orbital of  $In^{3+}$  ion in the IZO channel, the good interface matching of IZO/LaZrO, and the carrier blocking ability of PHPS-derived SiO<sub>2</sub> dielectric film. Therefore, the solution-processable LaZrO<sub>x</sub>/SiO<sub>2</sub> stack can be a promising candidate as a gate dielectric for low-temperature, high-performance, and low-cost flexible metal oxide FETs.

KEYWORDS: solution process, silicon dioxide, lanthanum zirconium oxide, indium zinc oxide, field-effect transistor, low temperature

# 1. INTRODUCTION

Transparent transition metal oxide (TMO) field-effect transistors (FETs) hold great promise for a range of electronic applications, including active-matrix liquid crystal displays (LCD), organic light-emitting diode displays (OLED), and flexible/transparent electronics owing to their high mobility, wide energy band gap (>3.0 eV), low temperature processing, good uniformity, and reasonable electrical stability. A variety of high-mobility TMO semiconductors, such as ZnO, InZnO, ZnSnO, InGaZnO, and InZnSnO, have been explored as channel materials using expensive vacuum-based deposition processes, such as sputtering, pulsed laser deposition, and atomic layer deposition.<sup>1–5</sup> In contrast, the solution processing of TMO semiconductors is a viable alternative because of the processing simplicity, low cost, and potentially high throughput. Therefore, low-temperature (<250 °C), solution-processable

Received: June 30, 2014 Accepted: October 6, 2014 Published: October 6, 2014 TMO TFTs have been developed by hydrolysis synthesis,<sup>6</sup> combustion process,<sup>7</sup> high pressure annealing,<sup>8</sup> and photo-chemical activation annealing.<sup>9</sup>

In contrast, solution-processable dielectric films have generally been overlooked in the search of high performance flexible TMO FETs, even though the semiconductor/insulator interface strongly affects charge transport, carrier trapping phenomena, and device instability. Thus far, the commercial production of InGaZnO FET-driven LCD and OLED display panels utilizes SiN<sub>x</sub> or SiO<sub>2</sub> films as a gate insulator deposited by plasma-enhanced chemical vapor deposition (PECVD) at high temperatures (>350 °C). The development of new gate dielectric materials that offer both solution processing and lowtemperature capability is an important and stringent objective for metal-oxide-based electronics, which enables the realization of low-cost flexible electronics, such as sensors, radio frequency identification tags, and backplane circuitry for active-matrix displays. For this reason, few studies have examined the solution processing of high-k dielectrics, such as  $Al_2O_{3,1}^{10,11}$  HfO<sub>2</sub>,<sup>12</sup> Y<sub>2</sub>O<sub>3</sub>,<sup>10,13</sup> and ZrO<sub>2</sub>,<sup>14–16</sup> for high-performance TFTs. The annealing temperature after the spin-coating of high-k metal oxide dielectrics has a profound effect on the electrical properties, which are affected significantly by unwanted impurities, such as carbon and hydroxyl group and uncompensated oxygen vacancies. High-temperature annealing  $(>300 \ ^{\circ}C)$ , which is one of the main bottlenecks of flexible electronics on plastic substrates, is effective in removing the impurities and oxygen vacancies from high-k dielectric films leading to acceptable leakage and capacitance characteristics.<sup>1</sup> Therefore, it is important to identify a facile route for preparing high-quality dielectrics at low temperatures (<250 °C) without performance loss of the resulting FETs.

An alternative approach would be to implement the organic dielectric as a gate insulator, which has good insulating properties, excellent solution processability, and low-temperature processing.<sup>18</sup> On the other hand, the chemical dissimilarity of the interface between the organic dielectric and TMO semiconductor hinders carrier transport and can be an origin of carrier trap sites, which gives rise to inferior mobility and adverse field-effect properties.<sup>19–22</sup> Recently, a hybrid nanodielectric film comprised of inorganic/self-assembly monolayer stacks was proposed as a promising candidate gate insulator for high-performance, low-temperature TMO FETs.<sup>23</sup> Although this hybrid concept offers high capacitance, reasonable leakage current, good interface compatibility, and low operation voltage, the preparation of inorganic high-k metal oxides still requires an expensive vacuum-deposition step.<sup>24</sup>

This study reports high-performance TMO FETs with a solution-processed SiO<sub>2</sub> dielectric that is curable at temperatures as low as 180 °C. The spin-coated SiO<sub>2</sub> film was prepared using a new precursor of perhydropolysilazane (PHPS), which is a spin-on dielectric composed of silicon and nitrogen. The hydrolysis and subsequent condensation of PHPS in the presence of a catalyst of 2-dimetylamino-1propanol (DMAPO) under humid conditions allowed the formation of high-quality SiO<sub>2</sub> films that exhibited good leakage characteristics, reasonable dielectric properties, and physical thickness controllability. To examine the interfacial compatibility between the solution-processable SiO<sub>2</sub> film and TMO semiconductor, FETs with an indium zinc oxide (IZO) channel layer were fabricated at the maximum process temperature of 180 °C. The bottom gate IZO FETs with the solutionprocessable SiO<sub>2</sub> dielectric can be produced to show an

apparent high field-effect mobility of 261.6 cm<sup>2</sup>/(V s), subthreshold gate swing (SS) of 0.45 V/decade, threshold voltage ( $V_{\rm TH}$ ) of -3.3 V, and current ( $I_{\rm ON/OFF}$ ) ratio of 2 × 10<sup>6</sup>. On the other hand, the SiO<sub>2</sub>-only gated device suffered from a larger leakage current and batch-to-batch parameter variations due to the hygroscopic nature of the silazane-derived SiO<sub>2</sub> film. The leakage current characteristics and operation stress stability of the IZO FETs can be improved further by introducing a high-k LaZrO<sub>x</sub> dielectric, which can also be prepared by simple spin-coating and low temperature annealing at 180 °C. The IZO FETs with a stack of LaZrO<sub>x</sub>/SiO<sub>2</sub> dielectric exhibited a low voltage driving of <5 V, a low SS factor of 0.16 V/decade, a high  $I_{\rm ON/OFF}$  ratio of 4 × 10<sup>7</sup>, and a hysteresis-free good stability, whereas the high mobility of 24.8 cm<sup>2</sup>/(V s) was still maintained.

#### 2. EXPERIMENTAL SECTION

2.1. Dielectric Film Preparation. The SiO<sub>2</sub> solution was prepared by dissolving perhydropolysilazane (PHPS, 1.90 M) and 2dimetylamino-1-propanol (C5H13NO, 0.05 M) in 10 mL of di-nbutyl ether (C<sub>8</sub>H<sub>18</sub>O). The 2-dimetylamino-1-propanol (DMAPO) was used as a catalyst to initiate the hydrolysis and condensation reactions, thereby facilitating the formation of an amorphous SiO2 network at low temperatures. The PHPS solution was spin-coated on bare Si substrates at 3000 rpm for 30 s. Before the PHPS coating, the bare Si was cleaned with acetone for 15 min followed by isopropyl alcohol for 15 min. The spin-coated PHPS films were baked on a hot plate for 5 min at 150 °C to remove the solvent. The PHPS films were then annealed under a moisture  $(H_2O)$  steam for 1 h at low temperatures of 180 and 250 °C. A precursor solution for the high-k LaZrO<sub>x</sub> dielectric was formulated by dissolving zirconium chloride  $(ZrCl_4, Aldrich)$  and lanthanum nitrate hexahydrate  $(La(NO_3)_3 \cdot 6H_2O_1)$ Aldrich) in ethanol, which was then stirred vigorously for 3 h at 50 °C until the solute had dissolved completely. The concentration of the precursor was 0.1 M, and the molar ratio of La/Zr was 1:2. The nitric acid and  $H_2O$  (1 M) were added as an oxidant into the LaZrO<sub>x</sub> precursor solution. The stirred LaZrO solution was filtered through a 0.2  $\mu$ m syringe filter. The LaZrO<sub>x</sub> dielectric films were spin-coated on a bare Si or PHPS-derived SiO $_2/Si$  substrate at 5000 rpm for 30 s, followed by drying at 100 °C on a hot plate for 10 min to eliminate the solvent. The LaZrO<sub>x</sub> films were annealed at 180, 250, 300, and 400 °C for 1 h under an electric furnace in an ambient atmosphere.

**2.2.** Material Characterization. The surface topography and roughness of the solution-processable dielectric films were analyzed by atomic force microscopy (AFM, JEOL, JSPM-5200) in tapping mode. The thickness of the SiO<sub>2</sub> and LaZrO<sub>x</sub> films was measured by scanning electron microscopy (SEM, Hitachi, S-4300) and transmission electron microscopy (TEM, JEOL, JEM-ARM200F). Fourier transform infrared (FTIR, Bruker, IFS66C/S, and HYPERION 3000) spectroscopy was used for the IR absorption spectra measurements of the PHPS-derived SiO<sub>2</sub> film, where bare silica glass was used as a reference. The chemical and structural properties of the PHPS-derived SiO<sub>2</sub> and LaZrO<sub>x</sub> dielectric films were examined by X-ray photoelectron spectroscopy (XPS, SIGMA PROBE, ThermoG, U.K.) and TEM, respectively.

**2.3. Device Fabrication and Characterization.** To examine the electrical properties, metal–insulator–metal capacitors were fabricated using sputter-deposited ITO top electrodes through a shadow mask with 100  $\mu$ m diameter holes. The capacitance–voltage (*C*–*V*) was measured using an HP 4284A impedance analyzer over the frequency range of 1–10<sup>3</sup> kHz. The dielectric leakage current ( $J_g$ ) was investigated using an HP 4140B picoammeter/DC voltage source. The ITO top electrode was biased while the Si substrate was grounded during the electrical measurements.

For the TMO FETs, a heavily doped p-type silicon wafer was used as the bottom gate electrode. The IZO thin film was deposited as the channel layer on the  $SiO_2/Si$ ,  $LaZrO_x/Si$  and  $LaZrO_x/SiO_2/Si$ substrates by direct current (dc) magnetron sputtering. The working

pressure and dc power during the sputtering of IZO (60 wt % In) were 100 W and 2 mTorr, respectively, under an Ar atmosphere. The ITO film as a source/drain (S/D) electrode was deposited using an identical sputtering system with an ITO target composition of 90 wt % In and 10 wt % Sn. During deposition of the ITO S/D electrode (90 wt % In), the working pressure and dc power were 5 mTorr and 50 W, respectively, under an Ar atmosphere. The width (*W*) and length (*L*) of the channel region in the fabricated IZO FETs were 100 and 150  $\mu$ m, respectively. The isolated channel and S/D electrodes were patterned through a shadow mask during sputtering deposition. The IZO FETs were annealed in air for 1 h at 180 °C. The electrical characteristics of the FETs were measured using a Keithley 2636 Source Meter at room temperature.

# 3. RESULTS AND DISCUSSION

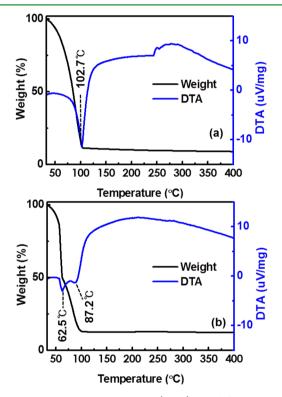

Thermogravimetric analysis (TGA) was performed to monitor the effects of the catalyst on the thermal decomposition behavior of the PHPS solution, as shown in Figure 1. The

**Figure 1.** Thermogravimetric analysis (TGA) and differential thermal analysis (DTA) curves of the PHPS solution (a) without and (b) with the catalyst of the 2-dimetylamino-1-propanol (0.6 wt %).

weight loss observed below 100 °C for the catalyst-free PHPS solution was attributed to the evaporation of both the solvent and organic molecules including nitrogen and hydrogen incorporated into the PHPS solution (Figure 1a). The endothermic reaction near ~102.7 °C in differential thermal analysis (DTA) can be attributed to the hydrolysis of Si–N bonds and the decomposition of PHPS macro-molecules. Interestingly, the PHPS solution with the DMAPO catalyst (0.6 wt %) was decomposed at temperatures lower than that of the PHPS film without a catalyst, which was consistent with the lower endothermic reaction temperature of 62.5 °C in the DTA data (Figure 1b). Therefore, it is expected that the nitrogen atom in the PHPS substance decomposed with the DMAPO catalyst and can be replaced by an oxygen atom from the air,

leading to the formation of Si–O bonds at low temperatures (<100  $^{\circ}$ C).

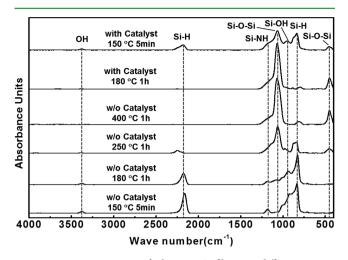

Figure 2 shows the FTIR spectra of the PHPS films at different curing temperatures. The spin-coated PHPS film

Figure 2. FTIR spectra of the PHPS films at different curing temperatures.

showed peaks at 835, 950, 2181, and 3377 cm<sup>-1</sup>, which were assigned to the Si-H wagging vibration, Si-H deformation, Si-H stretching, and O-H stretching bands, respectively.<sup>25,26</sup> This is understandable because PHPS is an inorganic oligomer  $(M_{\rm n} = 600-2000 \text{ g mol}^{-1}, M_{\rm w} = 1400-10000 \text{ g mol}^{-1})$ consisting of -SiH2NH- units. The bands assignable to the Si-O-Si asymmetric stretching transverse optical mode (1068 cm<sup>-1</sup>) and the Si-O-Si rocking mode (451 cm<sup>-1</sup>) were amplified significantly for the PHPS film cured at 400 °C, suggesting that the PHPS film is transformed completely to a condensed SiO<sub>2</sub> film. As the curing temperature was decreased to 180 °C, the intensity of the siloxane bond (Si-O-Si) and Si-H bond decreased drastically and increased, respectively. This suggests that it is difficult to form an amorphous Si-O network framework from traditional PHPS by low temperature curing (<250 °C). In contrast, the PHPS film from the solution with the DMAPO catalyst showed an FTIR spectrum similar to that of the SiO<sub>2</sub> film prepared at 400 °C. This clearly shows that the catalyst-assisted curing of the PHPS solution resulted in high-quality SiO<sub>2</sub> network formation at a low temperature of 180 °C.

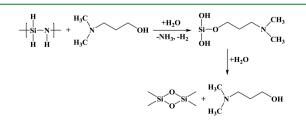

Figure 3 presents the catalyst-assisted thermal conversion of PHPS in the presence of moisture to  $SiO_2$ .<sup>27</sup> DMAPO is a well-known alkaline catalyst, in which the hydroxyl group (OH) and basicity can attack the Si–N and Si–H bond, respectively. Therefore, thermal annealing of the PHPS films with a

**Figure 3.** Schematic diagram showing the plausible reaction mechanism of the catalyst-assisted thermal conversion of PHPS in the presence of moisture to  $SiO_2$ .

DMAPO catalyst under moisture conditions cause efficient oxidation at low temperatures, which involve the hydrolysis of Si–N and S–H bonds leading to the release of NH<sub>3</sub> and H<sub>2</sub> and the formation of silanol groups. These intermediate silanol groups are converted to a SiO<sub>2</sub> network by a subsequent thermally initiated condensation process during thermal annealing.

Figure 4a shows the XPS survey spectra of the  $SiO_2$  films cured at 180 °C. The C 1s peak for C–C bonds was used to

**Figure 4.** (a) XPS survey spectra of the SiO<sub>2</sub> films cured at 180 °C. XP spectra of O 1s for the (b) catalyst-free and (c) catalyst-assisted SiO<sub>2</sub> film. XP spectra of Si 2p for the (d) catalyst-free and (e) catalyst-assisted SiO<sub>2</sub> film.

calibrate the photoelectron binding energy. The catalyst-free sample had N 1s, Si 2p, and O 1s peaks. The intensity of the N 1s and O 1s peaks for the catalyst-assisted SiO<sub>2</sub> film decreased and increased significantly, respectively, compared to those for the catalyst-free sample. In Figure 4, panels b and c present the O 1s XP spectra of the catalyst-free and -assisted SiO<sub>2</sub> films, respectively. The O 1s peaks can be deconvoluted into 531.7 and 532.6 eV. The peaks at 531.7 and 532.6 eV were assigned to the O–Si lattice peak and OH impurity, respectively.<sup>28</sup> The relative area of the O–Si-lattice-related peak for the catalyst-free and -assisted SiO<sub>2</sub> film were 54.0 and 62.8%, respectively,

as summarized in Table 1. In contrast, the hydroxyl group related peak area of the catalyst-assisted SiO<sub>2</sub> was diminished from 46.0 (catalyst-free SiO<sub>2</sub>) to 37.2%. In Figure 4, panels d and e show the Si 2p XPS for the catalyst-free and assisted SiO<sub>2</sub> films, respectively. In the case of the catalyst-free SiO<sub>2</sub> films, the rather broad Si 2p XPS can be deconvoluted into the SiO<sub>2</sub>,  $SiO_{xt}$  Si<sub>3</sub>N<sub>4</sub>, and SiC-related peaks, where their corresponding peak positions were 103.8, 102.8, 102.0, and 100.6 eV, respectively.<sup>29</sup> The impurity-related peaks, such as  $Si_3N_4$  and SiC bonding, disappeared in the Si 2p XP spectra of the catalysis-assisted SiO<sub>2</sub> film, as shown in Figure 4e. In addition, the SiO<sub>2</sub> and SiO<sub>x</sub> lattice peaks of the catalysis-assisted SiO<sub>2</sub> film increased and deceased substantially, respectively, compared to those of the catalysis-free SiO<sub>2</sub> film (also see Table 1). These results suggest that the DMAPO catalyst promotes the conversion of the silazane-based precursor to the condensed SiO<sub>2</sub> dielectric film, which supported the interpretation based on the FTIR result.

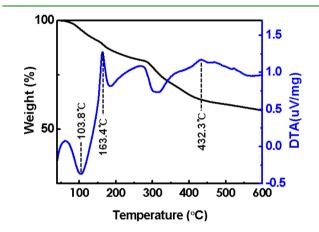

In this study, high-k LaZrO<sub>x</sub> films were also prepared by spin-coating a zirconium lanthanum oxide sol-gel solution followed by annealing at temperatures ranging from 180 to 400 °C. Here, the LaZrO<sub>x</sub> dielectric was chosen because the ZrO<sub>2</sub> and La<sub>2</sub>O<sub>3</sub> dielectrics have a wide band gap ( $\geq$ 5.5 eV) and high dielectric permittivity, allowing a low leakage current and low voltage driving. The cation composition ratio of La/Zr in the LaZrO<sub>x</sub> film was 0.32:0.68, which was determined by X-ray fluorescence spectroscopy. Figure 5 shows the TGA and DTA

Figure 5. TGA and DTA curves for the dried LaZrO<sub>x</sub> precursor.

data for the dried LaZrO<sub>x</sub> precursor. The small endothermic peak near 103.8 °C was assigned to the decomposition and hydrolysis of the metal precursors.<sup>15</sup> The sharp exothermic reaction at 163.4 °C indicates the metal-to-oxygen (M-O) formation at a low temperature. The reason for the M-O formation such a low temperature will be discussed below. The broad exothermic peak (>200 °C) suggests gradual densifica-

Table 1. Comparisons of the O 1s and Si 2p Peaks from the XPS Spectra of the Catalyst-Free and -Assisted SiO<sub>2</sub> Films

|                           | Si <sub>2p</sub>   |                     |                     | O <sub>1s</sub>     |                     |                     |

|---------------------------|--------------------|---------------------|---------------------|---------------------|---------------------|---------------------|

|                           | SiC                | $Si_xN_4$           | SiO <sub>x</sub>    | SiO <sub>2</sub>    | SiO <sub>2</sub>    | SiOH                |

| catalyst-free $SiO_2$     | 100.6 eV<br>(7.4%) | 102.0 eV<br>(41.6%) | 102.8 eV<br>(35.7%) | 103.8 eV<br>(15.3%) | 531.7 eV<br>(54.0%) | 532.6 eV<br>(46.0%) |

| catalyst-assisted $SiO_2$ |                    | (,                  | 102.8 eV<br>(28.6%) | 103.8 eV<br>(71.4%) | 531.7 eV<br>(62.8%) | 532.6 eV<br>(37.2%) |

tion. The exothermic reaction near 432.3  $^{\circ}$ C without weight loss corresponds to the crystallization of LaZrO<sub>x</sub>.

The insulating properties of the LaZrO<sub>x</sub> films prepared at the different annealing temperatures were examined by fabricating metal–insulator–metal capacitors. The gate leakage current density  $(J_g)$  versus the applied electric field (E) of the LaZrO<sub>x</sub> dielectrics on a heavily doped Si substrate was measured using an ITO top electrode, as shown in Figure 6a. For a better

**Figure 6.** (a) Gate leakage current density  $(J_g)$  vs applied electric field (E) of the capacitors with the LaZrO<sub>x</sub> dielectrics at different annealing temperatures. (b) XPS survey spectra of the LaZrO<sub>x</sub> dielectrics. (c) XP spectra of O 1s for the LaZrO<sub>x</sub> dielectrics.

comparison, the  $J_g$  values of both capacitors were plotted as a function of the thickness-normalized electric field. The capacitor with the LaZrO<sub>x</sub> dielectric film prepared at 400 °C exhibited the lowest  $J_g$  of  $8 \times 10^{-8}$  A/cm<sup>2</sup> at 1 MV/cm. The  $J_g$ of the LaZrO<sub>x</sub> capacitor increased with decreasing annealing temperature. On the other hand, the  $J_g$  of  $\sim 10^{-6}$  A/cm<sup>2</sup> at 1 MV/cm for the LaZrO<sub>x</sub> capacitor prepared at 180 °C was comparable to or even lower than those of the solution processed high-k dielectric capacitors prepared at the higher annealing temperature  $(\geq 400 \text{ °C})$ ,<sup>13,15,17</sup> which is acceptable for stable transistor operation. Figure 6b shows the XPS survey spectra of the solution-processable ZrLaO<sub>x</sub> films at different annealing temperatures. Zr 3d, La 3d, and O 1s peaks for all ZrLaO, films were clearly observed. Figure 6c shows the O 1s XPS of the LaZrO<sub>x</sub> films. The asymmetric O 1s peaks can also be deconvoluted into 531.3, 532.2, and 533.1 eV. The main lattice peak (531.3 eV) of O 1s is consistent with the typical O 1s peak position of stoichiometric ZrO<sub>2</sub> or La<sub>2</sub>O<sub>3</sub>. The peaks at 532.2 and 533.3 eV were assigned to the oxygen deficiency lattice peak and  $OH^-$  impurity, respectively.<sup>30</sup> The oxygen lattice and OH-related peaks of the LaZrO<sub>r</sub> film increased and decreased with increasing annealing temperature, suggesting

that the decomposition of metal precursor, hydrolysis, and condensation reactions are thermally activated (See Table S1, Supporting Information). This is consistent with the best insulating property of the resulting capacitor. In particular, the LaZrO, film prepared at a low temperature of 180 °C still exhibited a large peak area fraction ( $\sim$ 80%) for the oxygen lattice compared to those of the oxygen deficiency and OH impurity. The annealing temperature of the metal oxide film deposited by the sol-gel method depends strongly on the chemical bonding strength of the cation and oxygen ion, the ligand structure of metal precursor, and chemical additives.<sup>31,32</sup> The addition of a strong oxygen getter such as Ga reduces the annealing temperature for the solution-processable oxide materials because of its high bonding strength to the oxygen anion.<sup>33</sup> Similarly, the high bonding strength of Zr-O (776.1 kJ/mol) and La-O (1,170 kJ/mol) in this study would be beneficial to the formation of a M-O-M lattice at low temperatures.<sup>34,35</sup> Second, the annealing temperature required for the acetate-based precursor was reported to be higher  $(\geq 300$  °C) because the carbon residue remained in the resulting oxide film, even after high-temperature annealing.  $^{31,36,37}$  Carbon-free precursors such as zirconium chloride and lanthanum nitrate, which facilitates the efficient decomposition, hydrolysis, and condensation reaction, were used. In addition, nitric acid was added as an efficient oxidant because it easily decomposes to nitrogen dioxide and oxygen at low temperatures. This additional oxygen anion can accelerate the hydrolysis reaction of metal cations.<sup>38</sup>

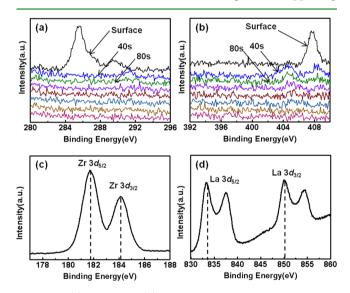

Figure 7a,b shows the depth profiles of carbon and nitrogen in the LaZrO<sub>x</sub> film at 180 °C (also see Figure S1, Supporting

Figure 7. (a) C 1s and (b) N 1s depth profiles of the  $LaZrO_x$  dielectrics film at 180 °C. XP spectra of (c) Zr 3d and (d) La 3d for the  $LaZrO_x$  film at 180 °C.

Information). Indeed, the carbon and nitrogen signals were detected only on the surface of the LaZrO<sub>x</sub> film due to the inevitable surface contamination. (Figure S1, Supporting Information). These adverse impurities were not observed in the bulk of the dielectric film, suggesting that the metal precursor cleanly decomposes, even at low temperatures without organic residues detectable by XPS. Third, chlorine (Cl) incorporation in the dielectric film would be advantageous for the low leakage characteristics. All dielectric films,

irrespective of the annealing temperatures, were in the chlorinated LaZrO<sub>x</sub> state. The atomic fraction of Cl in the LaZrO<sub>x</sub> films was 19.1-20.3%, whereas Cl ions existed uniformly in the LaZrO<sub>x</sub> films (Figure S1 and Table S2, Supporting Information). Halogen elements such as Cl or F are likely to inactivate the oxide charge trap state and reduce the fixed charges, leading to an improvement in the insulating properties of the resulting high-k dielectric oxide films such as HfO<sub>2</sub><sup>39,40</sup> and Al-doped ZrO<sub>2</sub>.<sup>41</sup> The similar beneficial behavior of the halogen elements has been reported for the IZO and ZTO channel materials in which the resulting TFTs exhibited better transporting and electrical stability.<sup>42,43</sup> Therefore, the superior leakage characteristic of the capacitor with the LaZrO<sub>x</sub> film annealed at a low temperature of 180 °C can be attributed to the following: (1) the high bonding strength of Zr-O and La $-O_{1}$  (2) the use of acetate-free metal precursors, and (3) halogen incorporation to the dielectric film. Figure 7c,d shows the Zr 3d and La 3d XP spectra of the LaZrO<sub>x</sub> film at 180 °C, respectively. No metallic peak was detected in the Zr 3d and La 3d spectra of the prepared ZrLaO<sub>x</sub> films. The peaks at 181.7 and 184.1 eV, as shown in Figure 7c, were assigned to Zr  $3d_{5/2}$ and 3d<sub>3/2</sub>, respectively, with a spin-orbit split of 2.4 eV, indicating the formation of ionic bonding between  $\mathrm{Zr}^{4\scriptscriptstyle+}$  and  $O^{2-.44}$  The magnitude (~4.4 eV) of multiplet splitting of La  $3d_{3/2}$  and  $3d_{5/2}$  suggests that the La cation is coordinated with  $O^{2-}$  ions (Figure 7d). From XPS, the LaZrO<sub>x</sub> film was confirmed to be a completely oxidized ionic substance with a Zr–O–La bond.<sup>4</sup>

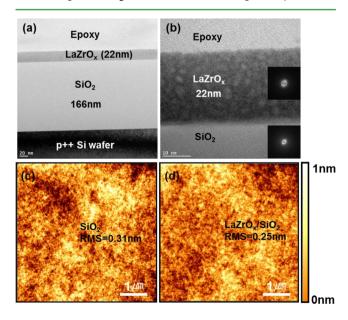

XTEM analysis further showed that the microstructures of the spin-coated  $SiO_2$  and  $LaZrO_x$  films were amorphous, which can be confirmed from the nanodiffraction patterns (Figure 8a, inset of Figure 8b, and Figure S2 in Supporting Information). The thickness of the SiO<sub>2</sub> and LaZrO<sub>x</sub> films prepared by the one-time spin-coating was 166 and 22 nm, respectively. Because

**Figure 8.** (a) Cross-sectional TEM image of  $LaZrO_x/SiO_2$  bilayer on Si substrate. (b) Enlarged XTEM image of the  $LaZrO_x/SiO_2$  dielectric film on the Si substrate. The insets show the corresponding nanodiffraction patterns of the  $LaZrO_x$  and  $SiO_2$  region with a diffuse ring. AFM images of spin-coated (c)  $SiO_2$  and (d)  $LaZrO_x/SiO_2$  film on Si substrate. The scale is  $5 \times 5 \mu$ m, and the height color scale is 0-2 nm.

the smooth dielectric/semiconductor interface is essential for the efficient transport of charge carriers in the FET device, the surface morphology and roughness were examined by AFM.

Figure 8c,d shows AFM images of the spin-coated SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> film on the Si substrate. Smooth surfaces were obtained for both films: the root-mean-square roughness values of the spin-coated SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> films were 0.31 and 0.25 nm, respectively. Therefore, the high carrier mobility in the resulting FETs on these dielectric interfaces can be anticipated due to the elimination of surface roughness-induced carrier scattering.

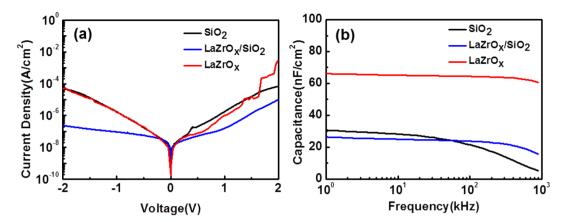

The insulating properties of the SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> films were assessed by fabricating metal-insulator-metal capacitors. Figure 9a shows the  $J_{\alpha}-E$  characteristics of the bare SiO<sub>2</sub> and  $LaZrO_x/SiO_2$  dielectrics on a heavily doped Si substrate. The spin-coated SiO<sub>2</sub> capacitor exhibited a reasonable  $J_{\sigma}$  (1.8 × 10<sup>-6</sup>  $A/cm^2$ ) at 1 MV/cm. The LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer capacitor showed a lower  $J_{\rm g}$  value of 1.6  $\times$   $10^{-7}~{\rm A/cm^2}$  at the same 1 MV/cm (also see Figure S3, Supporting Information). The superior insulating property of the bilayer capacitor can be used to achieve better performance of the IZO FETs. In addition, the gate dielectric breakdown field (~5 MV/cm) of the bilayer capacitor was higher than that (~4 MV/cm) of the  $SiO_r$ capacitor (data not shown). The superior insulating property of the bilayer dielectric film compared to the single-layer dielectric can be explained using the following rationale: The second coated  $LaZrO_x$  film in the bilayer dielectric film can fill the preexisting pinholes in the underlying SiO<sub>2</sub> film due to local dewetting of the solution film and/or unwanted contaminations on the substrate surface. Because these pinhole defects provide a local conducting path and increase the gate leakage current, the bilayer stack of the  $LaZrO_{r}/SiO_{2}$  films would result in the lower gate leakage characteristics compared to that of a single dielectric film. The similar improvement in the electrical properties using the hybrid stack was also reported in the field of organic or inorganic TFTs.<sup>46–48</sup>

Figure 9b shows the areal capacitance versus frequency characteristics of the bare  $SiO_2$  and  $LaZrO_r/SiO_r$  bilayer dielectrics capacitors. The capacitance of the bare SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer dielectrics at 10 kHz were  $\sim$ 28.2 and 25.0 nF/cm<sup>2</sup>, respectively. It is noted that the batch-to-batch variations (1 $\sigma$ ) of the capacitances for the SiO<sub>2</sub> and LaZrO<sub>x</sub>/ SiO<sub>2</sub> at 10 kHz were 27.6  $\pm$  3.3 and 23.8  $\pm$  2.5 nF/cm<sup>2</sup>, respectively (Figure S4, Supporting Information). It gives rise to the corresponding variations in the field-effect mobility for the IZO FETs with the  $SiO_2$  and  $LaZrO_x/SiO_2$  by approximately 13% and 12%, respectively (Figure S4, Supporting Information). The slightly lower capacitance of the  $LaZrO_x/SiO_2$  bilayer dielectrics can be understood by considering a series capacitor model  $(1/C_{total} = 1/C_{SiO_2} +$  $C_{LaZrO_x}$ ). The extracted relative dielectric constant of the spincoated  $SiO_2$  and  $LaZrO_r$  film were 5.3 and 11.8, respectively.

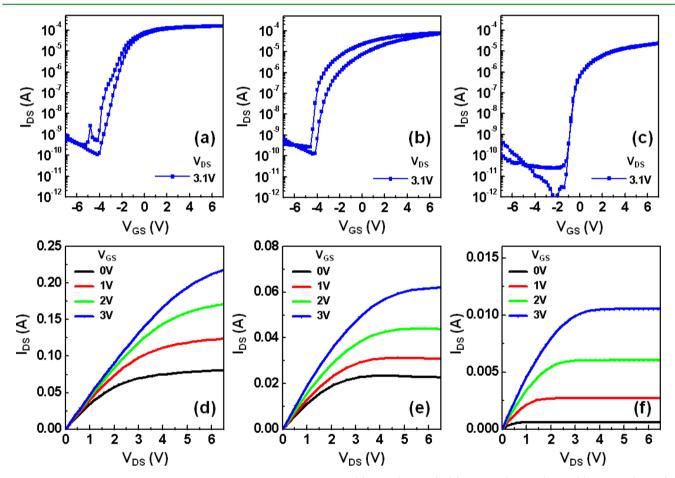

IZO FETs with SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer insulators were fabricated. In Figure 10, panels a and c show the transfer characteristics of the IZO FETs with SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer insulators, respectively. The field-effect mobility ( $\mu_{FE}$ ) was determined from the incremental slope of the  $I_{DS}^{-1/2}$  versus  $V_{GS}$  plot in the saturation region using the following equation:

$$I_{\rm DS} = (WC_i/2L)\mu_{\rm FE}(V_{\rm GS} - V_{\rm TH})^2 V_{\rm DS}$$

(1)

where *L* is the channel length, *W* is the width, and  $C_i$  is the gate capacitance per unit area.  $V_{\text{TH}}$  was defined as the gate voltage

Figure 9. (a)  $J_g - E$  characteristics of bare SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> dielectrics on a heavily doped Si substrate. (b) Areal capacitance vs frequency characteristics of bare SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer dielectrics capacitors.

**Figure 10.** Representative transfer characteristics of the IZO FETs with the (a)  $SiO_2$  (166 nm), (b)  $LaZrO_x$  (160 nm), and (c)  $LaZrO_x$  (22 nm)/ SiO<sub>2</sub> (166 nm) bilayer insulators. Representative output characteristics of the IZO FETs with the (d)  $SiO_2$ , (e)  $LaZrO_x$ , and (f)  $LaZrO_x/SiO_2$  bilayer insulators.

| Table 2. Electrical Characteristics of FETs based on Different Gat | ate Insulators" |

|--------------------------------------------------------------------|-----------------|

|--------------------------------------------------------------------|-----------------|

| FET samples                                                                                                                                                     | $M_{Fe}  (cm^2 V^{-1} S^{-1})$ | SS (V/decade) | $V_{\rm TH}$ (V) | $I_{\rm ON}/I_{\rm OFF}$ | $N_{\rm IT}~({\rm cm}^{-2})$ | $\Delta v_{Hysteresis}$ (V) |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------|---------------|------------------|--------------------------|------------------------------|-----------------------------|--|--|

| SiO <sub>2</sub>                                                                                                                                                | 261.6                          | 0.45          | -3.3             | $2 \times 10^{6}$        | $2.1 \times 10^{12}$         | 0.66                        |  |  |

| $LaZrO_x$                                                                                                                                                       | 45.8                           | 0.27          | -3.7             | $8 \times 10^{5}$        | $1.8 \times 10^{12}$         | 0.8                         |  |  |

| LaZrO <sub>x</sub> /SiO <sub>2</sub>                                                                                                                            | 24.8                           | 0.16          | -0.8             | $4 \times 10^{7}$        | $4.1 \times 10^{11}$         | ~0                          |  |  |

| $^{a}$ The uniformity of the transfer characteristics for the SiO <sub>2</sub> and bilayer-gated IZO FETs are also shown in Figure S5 (Supporting Information). |                                |               |                  |                          |                              |                             |  |  |

that induces a drain current of 1 nA at  $V_{\rm DS}$  = 3.1 V. The subthreshold gate swing [SS =  $dV_{\rm GS}/(d \log I_{\rm DS}) (V/\text{decade})$ ]

was extracted from the linear part of the  $log(I_{DS})$  versus  $V_{GS}$  plot. The IZO FETs with a SiO<sub>2</sub> gate insulator showed

promising performance with a high  $\mu_{\rm FE}$  of 261.6 cm<sup>2</sup>/(V s), a SS of 0.45 V/decade, a  $V_{\rm TH}$  of -3.25 V, and a  $I_{\rm ON/OFF}$  ratio of 2  $\times$  10<sup>6</sup>, as summarized in Table 2. The exceptional apparent high mobility for the SiO<sub>2</sub> gated IZO FET should be considered carefully. The field-effect mobility extracted in this study was determined by the V<sub>GS</sub>-dependent drain current variation. In the case of a relatively leaky dielectric film, the gate leakage current is reflected in the drain current, which amplifies the field-effect mobility. The possibility of n-type doping due to the reaction of a hygroscopic SiO<sub>2</sub> film cannot be excluded as a plausible reason for this high mobility. The water molecules that were taken up by the hygroscopic silazane-derived SiO<sub>2</sub> film can increase the electron carrier density of the IZO channel layer because they can play the role as an electron donor in the Zn-based oxide film.<sup>49</sup> Thus, the hygroscopic SiO<sub>2</sub>-gated IZO FETs showed large batch-to-batch variations in terms of device parameters such as  $\mu_{\rm FE}$ , SS,  $V_{\rm TH}$ , and  $I_{\rm ON/OFF}$  ratio (see Figure S5, Supporting Information). The pixel switching or driving FETs in the practical active-matrix flexible display requires high mobility and extremely low leakage drain current (<10 pA). In the case of mobile display/electronics, the leakage drain current  $(I_{OFF})$  should be kept to a minimum because it adversely affects the power consumption. Unfortunately, the  $I_{OFF}$  of IZO FETs with a SiO<sub>2</sub> dielectric was rather large ( $\sim$ 80 pA), which requires improvement. In contrast, significant improvement in terms of  $I_{\rm OFF}$ , SS, and  $I_{\rm ON/OFF}$  ratio was observed for the IZO FETs with a LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer dielectric: I<sub>OFF</sub>, SS, and I<sub>ON/OFF</sub> ratio were improved to 2 pA, 0.16 V/decade, and 4  $\times$  10<sup>7</sup>, respectively, whereas a high mobility of 24.8  $\text{cm}^2/(\text{V s})$  was still maintained. In addition, the batch-to-batch parameter variations for the IZO FETs with a LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer dielectric were diminished compared to those with a single SiO<sub>2</sub> dielectric (See Figure S5, Supporting Information). The high mobility and good  $I_{\rm ON/OFF}$  ratio of the IZO FETs with a LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer at 180 °C can be attributed to the low effective electron mass in an indium-based oxide, the efficient intercalation (percolation path) of the 5s orbital of In<sup>3+</sup> ion, the good insulating property of the bilayer dielectric film, and the smooth  $IZO/LaZrO_x$  interface. Figure 10d,f shows the representative output characteristics of the IZO FET with the  $SiO_2$  and  $LaZrO_x/SiO_2$  bilayer insulators, respectively. The clear pinch-off for both devices suggests that electron transport in the IZO active channel was controlled by the gate and drain voltages. In addition, the absence of crawling in the  $I_{\rm DS}$  in the low  $V_{\rm DS}$  voltage region suggested Ohmic contact between the IZO channel and ITO source/drain electrode.

The operational device stability of a given FET is often characterized by the amount of hysteresis between the forward and reverse sweep. In the case of IZO FETs with a SiO<sub>2</sub> dielectric, clockwise hysteresis phenomena ( $\Delta V_{\rm TH}$  = 0.66 V) were observed, as shown in Figure 10a. This hysteresis can be attributed to either carrier trapping at the interfacial trap states or carrier injection to the bulk region of the underlying dielectric film under the accumulation mode. The hydroxyl group in the oxide dielectric film is the carrier trapping center.<sup>50–52</sup> The presence of a hydroxyl group in the polymerderived gate dielectric for the organic TFTs was also reported to accelerate the charge trapping phenomena for the transporting carriers, hence the hysteresis instability.<sup>53-58</sup> Therefore, the high concentration of the hydroxyl group in the silazanederived SiO<sub>2</sub> dielectric film would be responsible for the interior hysteresis behavior. For this reason, the resistance of the SiO<sub>2</sub>-gated IZO FETs upon humidity exposure is expected

to be low due to the hygroscopic behavior of the silazanederived SiO<sub>2</sub> material. In contrast, this hysteresis was reduced substantially in the IZO FETs with a LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer dielectric, suggesting a decrease in the interfacial trap states by the introduction of a high-k LaZrO<sub>x</sub> dielectric (see Figure 10c). The denser LaZrO<sub>x</sub> film in the bilayer dielectric film may alleviate the adverse direct carrier trapping from the channel region to the bulk region of SiO<sub>2</sub> film. On the other hand, the pinhole-less or free structure in the hybrid stack can contribute partially to the reduction in the hysteresis. This synergic effect of the bilayer dielectric structure compared to the single layer dielectric structure in terms of the reduced gate leakage current and hysteresis has been also reported for organic thin-film transistors (TFTs).<sup>59</sup> The interfacial traps density (N<sub>it</sub>) was calculated using the following equation from the subthreshold swing:<sup>60</sup>

$$N_{\rm it} = [SS\log(e)/(k_{\rm B}T/q) - 1]\frac{C_i}{q}$$

<sup>(2)</sup>

where q is the electron charge,  $k_{\rm B}$  is the Boltzmann constant, and T is the absolute temperature. The calculated  $N_{\rm it}$  value for the IZO FETs with a SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> dielectric were 2.4 × 10<sup>12</sup> and 4.1 × 10<sup>11</sup> /cm<sup>2</sup>, respectively. Therefore, the superior operational stability of the IZO FETs with a bilayer dielectric is well corroborated with the lower  $N_{\rm it}$  value. This suggests that the role of the LaZrO<sub>x</sub> dielectric is to provide better interface matching between the IZO channel layer and gate dielectric layer, thereby allowing a decreased  $N_{\rm it}$  value and good operational stability of the resulting FETs.

Generally, high-k dielectrics such as HfO2, ZrO2, La2O3 are preferred as a gate insulator owing to their excellent charge coupling capability, which results in a decreasing SS factor and low operating voltage. On the other hand, the high-k dielectric suffered from a high leakage current and low breakdown voltage because they have a lower band gap and smaller band offsets to the metal oxide semiconductor compared to SiO<sub>2</sub> or Al<sub>2</sub>O<sub>3</sub> dielectrics.<sup>61,62</sup> These adverse electrical properties can be aggravated further by the polycrystalline nature, where the grain boundary defects act as a leakage current path. In this regard, this study also examined the device performance of the IZO FETs with a  $LaZrO_r$ -only gate insulator, where the LaZrO<sub>r</sub> films of greater thickness ( $\sim$ 160 nm) can be obtained by 6 times spin-on deposition and annealing at 180 °C. Although a high mobility of 45.8  $\text{cm}^2/(\text{V s})$  was obtained, they suffered from a larger  $I_{\text{OFF}}$  value (100 pA) and inferior hysteresis ( $\Delta V_{\rm TH}$  = 0.8 V; Figure 10b). Therefore, the promising performance of the IZO FETs with a LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer dielectric is the synergistic effects of the PHPS-derived SiO<sub>2</sub> film with good bulk property and a sol-gel-derived LaZrO<sub>x</sub> film with better interfacial matching. Many studies have emphasized the high mobility (>50  $\text{cm}^2/(\text{V s})$ ) of the TMO TFTs.<sup>13,63-66</sup> On the other hand, the  $I_{OFF}$  values reported in those studies were rather high (>100 pA),<sup>62-65</sup> which is unacceptable for practical applications as a pixel driver. Therefore, the compromise between the field-effect mobility and  $I_{OFF}$  values achieved for the IZO FETs through the introduction of a LaZrO<sub>x</sub>/SiO<sub>2</sub> bilayer gate dielectric will have technical implications for the realization of flexible, low-cost electronics.

# 4. CONCLUSION

This study showed that a PHPS-derived SiO<sub>2</sub> film capped with a LaZrO<sub>x</sub> dielectric film affords a smooth, pinhole-free dielectric material with high-capacitance and good insulating properties. This bilayer stack can be readily deposited from solution at a low temperature of 180 °C, which can be compatible with the plastic substrate. The resulting IZO FETs with a stack of LaZrO<sub>x</sub>/SiO<sub>2</sub> dielectric exhibited a high mobility of 24.8 cm<sup>2</sup>/ (V s), a low voltage driving of <5 V, a low SS factor of 0.16 V/ decade, a high  $I_{\text{ON/OFF}}$  ratio of  $4 \times 10^7$ , and good hysteresis-free stability. Therefore, the solution-based LaZrO<sub>x</sub>/SiO<sub>2</sub> dielectric stack is an attractive candidate as a solution-processable gate dielectric for high-performance, low-cost, and flexible TMO FETs.

# ASSOCIATED CONTENT

#### **S** Supporting Information

Deconvolution data of XPS O1s peaks, concentration depth profiles and X-ray diffraction patterns for various LaZrO<sub>x</sub> films; statistical data on the J-E and C-f of SiO<sub>2</sub> and LaZrO<sub>x</sub>/SiO<sub>2</sub> capacitors and the corresponding transfer characteristics of IZO FETs. This material is available free of charge via the Internet at http://pubs.acs.org.

# AUTHOR INFORMATION

#### Corresponding Author

\*E-mail: jkjeong@inha.ac.kr.

#### Notes

The authors declare no competing financial interest.

#### ACKNOWLEDGMENTS

This study was supported by the Industrial Strategic Technology Development Program funded by the Ministry of Knowledge Economy, Korea Evaluation Institute of Industrial Technology (MKE/KEIT) under Grants 10041808 and 10041041.

#### REFERENCES

(1) Nomura, K.; Ohta, H.; Takagi, A.; Kamiya, T.; Hirano, M.; Hosono, H. Room-Temperature Fabrication of Transparent Flexible Thin-Film Transistors using Amorphous Oxide Semiconductors. *Nature* **2004**, *432*, 488–492.

(2) Chiang, H. Q.; Wager, J. F.; Hoffman, R. L.; Jeong, J.; Keszler, D. A. High Mobility Transparent Thin-Film Transistors with Amorphous Zinc Tin Oxide Channel Layer. *Appl. Phys. Lett.* **2005**, *86*, 013503.

(3) Fortunato, E.; Barquinha, P.; Martins, R. Oxide Semiconductor Thin-Film Transistors: A Review of Recent Advances. *Adv. Mater.* **2012**, *24*, 2945–2986.

(4) Park, J. S.; Maeng, W. J.; Kim, H. S. Review of Recent Developments in Amorphous Oxide Semiconductor Thin-Film Transistor Devices. *Thin Solid Films* **2012**, *520*, 1679–1693.

(5) Jeong, J. K. Photo-Bias Instability of Metal Oxide Thin Film Transistors for Advanced Active Matrix Display. *Semicond. Sci. Technol.* **2011**, *26*, 034008.

(6) Banger, K. K.; Yamashita, Y.; Mori, K.; Peterson, R. L.; Leedham, T.; Richard, J.; Sirringhaus, H. Low-Temperature, High-Performance Solution-Processed Metal Oxide Thin-Film Transistors Formed by a 'Sol–Gel on Chip' Process. *Nat. Mater.* **2011**, *10*, 45–50.

(7) Kim, M.-G.; Kanatzidis, M. G.; Facchett, A.; Marks, T. J. Low-Temperature Fabrication of High-Performance Metal Oxide Thin-Film Electronics via Combustion Processing. *Nat. Mater.* **2011**, *10*, 382– 388.

(8) Rim, Y. S.; Jeong, W. H.; Kim, D. L.; Lim, H. S.; Kim, K. M.; Kim, H. J. Simultaneous Modification of Pyrolysis and Densification for Low-Temperature Solution-Processed Flexible Oxide Thin-Film Transistors. J. Mater. Chem. 2012, 22, 12491–12497.

(9) Kim, Y. H.; Heo, J. S.; Kim, T. H.; Park, S.; Yoon, M. H.; Kim, J.; Oh, M. S.; Yi, G. R.; Noh, Y. Y.; Park, S. K. Flexible Metal-Oxide Devices Made by Room-Temperature Photochemical Activation of Sol-Gel Films. *Nature* **2012**, *489*, 128–132.

(10) Adamopoulos, G.; Thomas, S.; Bradley, D. D. C.; McLachlan, M. A.; Anthopoulos, T. D. Low-Voltage ZnO Thin-Film Transistors Based on  $Y_2O_3$  and  $Al_2O_3$  High-k Dielectrics Deposited by Spray Pyrolysis in Air. *Appl. Phys. Lett.* **2011**, *98*, 123503.

(11) Avis, C.; Jin, J. High-Performance Solution Processed Oxide TFT with Aluminum Oxide Gate Dielectric Fabricated by a Sol–Gel Method. J. Mater. Chem. 2011, 21, 10649–10652.

(12) Avis, C.; Kim, Y. G.; Jang, J. Solution Processed Hafnium Oxide as a Gate Insulator for Low-Voltage Oxide Thin-Film Transistors. *J. Mater. Chem.* **2012**, *22*, 17415–17420.

(13) Song, K.; Yang, W.; Jung, Y.; Jeong, S.; Moon, J. A Solution-Processed Yttrium Oxide Gate Insulator for High-Performance All-Solution-Processed Fully Transparent Thin Film Transistors. *J. Mater. Chem.* **2012**, *22*, 21265–21271.

(14) Xu, X.; Cui, Q.; Jin, Y.; Guo, X. Low-Voltage Zinc Oxide Thin-Film Transistors with Solution-Processed Channel and Dielectric Layers below 150 °C. *Appl. Phys. Lett.* **2012**, *101*, 222114.

(15) Park, J. H.; Yoo, Y. B.; Lee, K. H.; Jang, W. S.; Oh, J. Y.; Chae, S. S.; Baik, H. K. Low-Temperature, High-Performance, Solution-Processed Thin-Film Transistors with Peroxo-Zirconium Oxide Dielectric. *ACS Appl. Mater. Interfaces* **2013**, *5*, 410–417.

(16) Lee, C.; Dodabalapur, A. Solution-Processed Zinc-Tin Oxide Thin-Film Transistors with Low Interfacial Trap Density and Improved Performance. *Appl. Phys. Lett.* **2010**, *96*, 243501.

(17) Son, B.; Je, S. Y.; Kim, H. J.; Lee, C.; Lee, C.; Hwang, A. Y.; Won, J. Y.; Song, J. H.; Choi, R.; Jeong, J. K. High-Performance In–Zn–O Thin Film Transistors with a Soluble Processed  $ZrO_2$  Gate Insulator. *Phys. Status Solidi RRL* **2013**, *7*, 485–488.

(18) Bao, Z.; Locklin, J. Organic Field-Effect Transistors; CRC Press: Boca Raton, FL, 2007.

(19) Jang, K. S.; Wee, D.; Kim, Y. H.; Kim, J.; Ahn, T.; Ka, J. W.; Yi, M. H. Surface Modification of a Polyimide Gate Insulator with an Yttrium Oxide Interlayer for Aqueous-Solution-Processed ZnO Thin-Film Transistors. *Langmuir* **2013**, *29*, 7143–7150.

(20) Nakata, M.; Sato, H.; Nakajima, Y.; Tsuji, H.; Fujisaki, Y.; Takei, T.; Yamamoto, T.; Fujikake, H. Analysis of the Influence of Sputtering Damage to Polymer Gate Insulators in Amorphous InGaZnO<sub>4</sub> Thin-Film Transistors. *Jpn. J. Appl. Phys.* **2012**, *51*, 044105.

(21) Jung, Y.; Jun, T.; Kim, A.; Song, K.; Yeo, T. H.; Moon, J. Direct Photopatternable Organic–Inorganic Hybrid Gate Dielectric for Solution-Processed Flexible ZnO Thin Film Transistors. *J. Mater. Chem.* **2011**, *21*, 11879–11885.

(22) Hwang, D. K.; Park, J. H.; Lee, J.; Choi, J. M.; Kim, J. H.; Kim, E.; Im, S. Pentacene-Based TTFTs with Polymer Gate Dielectric and NiO<sub>x</sub> Electrodes. *Electrochem. Solid-State Lett.* **2005**, *8*, G140.

(23) Liu, J.; Buchholz, B.; Chang, R. P. H.; Facchetti, A.; Mark, T. J. High-Performance Flexible Transparent Thin-Film Transistors Using a Hybrid Gate Dielectric and an Amorphous Zinc Idium Tin Oxide Channel. *Adv. Mater.* **2010**, *22*, 2333–2337.

(24) Park, Y. M.; Desai, A.; Salleo, A. Solution-Processable Zirconium Oxide Gate Dielectrics for Flexible Organic Field Effect Transistors Operated at Low Voltages. *Chem. Mater.* **2013**, *25*, 2571–2579.

(25) Yamano, A.; Kozuka, H. Preparation of Silica Coatings Heavily Doped with Spiropyran Using Perhydropolysilazane as the Silica Source and Their Photochromic Properties. *J. Phys. Chem. B* **2009**, *113*, 5769–5776.

(26) Prager, L.; Dierdorf, A.; Liebe, H.; Naumov, S.; Stojanovic, S.; Heller, R.; Wennrich, L.; Buchmeiser, M. R. Conversion of Perhydropolysilazane into a SiO<sub>x</sub> Network Triggered by Vacuum Ultraviolet Irradiation: Access to Flexible, Transparent Barrier Coatings. *Chem.*—*Eur. J.* **2007**, *13*, 8522–8529.

(27) Bauer, F.; Decker, U.; Dierdorf, A.; Ernst, H.; Heller, R.; Liebe, H.; Mehnert, R. Preparation of Moisture Curable Polysilazane

Coatings. Part I. Elucidation of Low Temperature Curing Kinetics by FT-IR Spectroscopy. Prog. Org. Coat. 2005, 53, 183–190.

(28) Kim, Y. H.; Lee, D. K.; Cha, H. G.; Kim, C. W.; Kang, Y. C.; Kang, Y. S. Preparation and Characterization of the Antibacterial Cu Nanoparticle Formed on the Surface of SiO<sub>2</sub> Nanoparticles. *J. Phys. Chem. B* **2006**, *110*, 24923–24928.

(29) Wagner, C. D.; Passoja, D. E.; Hillery, H. F.; Kinisky, T. G.; Six, H. A.; Jansen, W. T.; Taylor, J. A. Auger and Photoelectron Line Energy Relationships in Aluminum-Oxygen and Silicon-Oxygen Compounds. J. Vac. Sci. Technol. **1982**, 21, 933–944.

(30) Yue, L.; Pu, H.; Pang, S.; Li, H.; Zhang, Q. Top-Gate LZTO Thin-Film Transistors with PMMA Gate Insulator by Solution Process. *Europhys. Lett.* **2012**, *97*, 67006.

(31) Kim, S. J.; Yoon, S.; Kim, H. J. Review of Solution-Processed Oxide Thin-Film Transistors. *Jpn. J. Appl. Phys.* **2014**, *53*, 02BA02.

(32) Jeong, S.; Moon, J. Low-Temperature, Solution-Processed Metal Oxide Thin Film Transistors. J. Mater. Chem. **2012**, 22, 1243–1250.

(33) Jeong, S.; Ha, Y.-G.; Moon, J.; Facchetti, A.; Marks, T. J. Role of Gallium Doping in Dramatically Lowering Amorphous-Oxide Processing Temperatures for Solution-Derived Indium Zinc Oxide Thin-Film Transistors. *Adv. Mater.* **2009**, *22*, 1346–1350.

(34) Hennek, J. W.; Smith, J.; Yan, A.; Kim, M.-G.; Zhao, W.; Dravid, V. P.; Facchetti, A.; Marks, T. J. Oxygen "Getter" Effects on Microstructures and Carrier Transport in Low Temperature Combustion-Processed a-InXZnO (X = Ga, Sc, Y, La) Transistors. *J. Am. Chem. Soc.* **2013**, *135*, 10729–10741.

(35) Kerr, J. A. In CRC Handbook of Chemistry and Physics: A Ready-Reference Book of Chemical and Physical Data (CRC Handbook of Chemistry and Physics); Lide, D. R., Ed. CRC press, Boca Raton, FL, 2000.

(36) Kim, Y. J.; Yang, B. S.; Oh, S.; Han, S. J.; Lee, H. W.; Heo, J.; Jeong, J. K.; Kim, H. J. Photobias Instability of High Performance Solution Processed Amorphous Zinc Tin Oxide Transistors. *ACS Appl. Mater. Interfaces* **2013**, *5*, 3255–3261.

(37) Jeong, S.; Jeong, Y.; Moon, J. Solution-Processed Zinc Tin Oxide Semiconductor for Thin-Film Transistors. J. Phys. Chem. C 2008, 112, 11082–11085.

(38) Jeong, W. H.; Kim, D. L.; Kim, H. J. Accelerated Formation of Metal Oxide Thin Film at 200 °C Using Oxygen Supplied by a Nitric Acid Additive and Residual Organic Suction Vacuum Annealing for Thin-Film Transistor Applications. *ACS Appl. Mater. Interfaces* **2013**, *5*, 9051–9056.

(39) Seo, K.-I.; Screenivasan, R.; McIntyre, P. C.; Saraswat, K. C. Improvement in High-k ( $HfO_2/SiO_2$ ) Reliability by Incorporation of Fluorine. *IEEE Electron Device Lett.* **2006**, *27*, 821–823.

(40) Chen, Y.-T.; Zhao, H.; Wang, Y.; Xue, F.; Zhou, F.; Lee, J. C. Fluorinated  $HfO_2$  Gate Dielectric Engineering on  $In_{0.53}Ga_{0.47}As$  Metal-Oxide-Semiconductor Field-Effect-Transistors. *Appl. Phys. Lett.* **2010**, *96*, 103506.

(41) Yang, W.; Song, K.; Jung, Y.; Jeong, S.; Moon, J. Solution-Deposited Zr-Doped AlO<sub>x</sub> Gate Dielectrics Enabling High-Performance Flexible Transparent Thin Film Transistors. *J. Mater. Chem. C* **2013**, *1*, 4275–4282.

(42) Avis, C.; Jang, J. A. High Performance Inkjet Printed Zinc Tin Oxide Transparent Thin-Film Transistor Manufactured at the Maximum Process Temeprature of 300 °C and Its Stability Test. *Electrochem. Solid-State Lett.* **2011**, *14*, J9–J11.

(43) Seo, J.-S.; Jeon, J.-H.; Hwang, Y. H.; Park, H.; Ryu, M.; Park, S.-H. K.; Bae, B.-S. Solution-Processed Flexible Fluorine-Doped Indium Zinc Oxide Thin-Film Transistors Fabricated on Plastic Film at Low Temperature. *Sci. Rep.* **2013**, *3*, 2085.

(44) Moulder, J. F.; Stickle, W. F.; Sobol, P. E.; Bomber, K. D. Handbook of X-ray Photoelectron Spectroscopy: Reference Book of Standard Spectra for Identification and Interpretation of XPS Data; Physical Electronics, Inc.: Chanhassen, MN, 1995.

(45) Han, C. Y.; Qian, L. X.; Leung, C. H.; Che, C. M.; Lai, P. T. High-Performance Pentacene Thin-Film Transistor with ZrLaO Gate Dielectric Passivated by Fluorine Incorporation. *Org. Electron.* **2013**, *14*, 2973–2979.

(46) Yoon, M.-H.; Facchetti, A.; Marks, T. J. s-p Molecular Dielectric Multilayers for Low-Voltage Organic Thin-Film Transistors. *Proc. Natl. Acad. Sci. U.S.A.* **2005**, *102*, 4678–4682.

(47) Ma, H.; Yip, H.-L.; Huang, F.; Jen, A. K.-Y. Interface Engineering for Organic Electronics. *Adv. Funct. Mater.* **2010**, *20*, 1371–1388.

(48) Kim, D. J.; Kim, D. L.; Rim, Y. S.; Kim, C. H.; Jeong, W. H.; Lim, H. S.; Kim, H. J. Improved Electrical Performance of an Oxide Thin-Film Transistor Having Multistacked Active Layers Using a Solution Process. ACS Appl. Mater. Interfaces **2012**, *4*, 4001–4005.

(49) Park, J. S.; Jeong, J. K.; Chung, H.-J.; Mo, Y. G.; Kim, H. D. Electronic Transport Properties of Amorphous Indium–Gallium– Zinc Oxide Semiconductor upon Exposure to Water. *Appl. Phys. Lett.* **2008**, *92*, 072104.

(50) Kim, C. S.; Jo, S. J.; Lee, S. W.; Kim, W. J.; Baik, H. K.; Lee, S. J. Surface-Modified High-k Oxide Gate Dielectric for Low-Voltage High-Performance Pentacene Thin-Film Transistor. *Adv. Funct. Mater.* **2007**, *17*, 958–962.

(51) Chua, L.-L.; Zaumseil, J.; Chang, J.-F.; Ou, E. C.-W.; Ho, P. K.-H.; Sirringhaus, H.; Friend, R. H. General Observation of n-Type Field-Effect Behavior in Organic Semiconductors. *Nature* **2005**, *434*, 194–199.

(52) Gdula, R. A. The Effects of Processing on Hot Electron Trapping in SiO<sub>2</sub>. J. Electrochem. Soc. **1976**, 123, 42–47.

(53) Tsai, T.-D.; Chang, J.-W.; Wen, T.-C.; Guo, T.-F. Manipulating the Hysteresis in Poly(vinyl alcohol)-Dielectric Organic Field-Effect Transistors Toward Memory Elements. *Adv. Mater.* **2013**, *23*, 4206– 4214.

(54) Singh, T. B.; Marjanović, N.; Matt, G. J.; Sariciftci, N. S.; Schwödiauer, R.; Bauer, S. Nonvolatile Organic Field-Effect Transistor Memory Element with a Polymeric Gate Electret. *Appl. Phys. Lett.* **2004**, *85*, 5409.

(55) Egginger, M.; Vladu, M. I.; Schwödiauer, R.; Tanda, A.; Frischauf, I.; Bauer, S.; Sariciftci, N. S. Mobile Ionic Impurities in Poly(vinyl alcohol) Gate Dielectric: Possible Source of the Hysteresis in Organic Field-Effect Transistors. *Adv. Mater.* **2008**, *20*, 1018–1022.

(56) Orgiu, E.; Locci, S.; Fraboni, B.; Scavetta, E.; Lugli, P.; Bonfiglio, A. Analysis of the Hysteresis in Organic Thin-Film Transistors with Polymeric Gate Dielectric. *Org. Electron.* **2011**, *12*, 477–485.

(57) Hwang, D. K.; Lee, K.; Kim, J. H.; Im, S.; Park, J. H.; Kim, E. Comparative Studies on the Stability of Polymer versus SiO<sub>2</sub> Gate Dielectrics for Pentacene Thin-Film Transistors. *Appl. Phys. Lett.* **2006**, *89*, 093507.

(58) Lee, S.; Koo, B.; Shin, J.; Lee, E.; Park, H.; Kim, H. Effects of Hydroxyl Groups in Polymeric Dielectrics on Organic Transistor Performance. *Appl. Phys. Lett.* **2006**, *88*, 162109.

(59) Wang, G.; Moses, D.; Heeger, A. J.; Zhang, H.-M.; Narasimhan, M.; Demaray, R. E. Poly(3-hexylthiophene) Field-Effect Transistors with High Dielectric Constant Gate Insulator. *J. Appl. Phys.* **2004**, *95*, 316–322.

(60) Kagan, C. Y.; Andry, P. W. E. Thin Film Transistors; Dekker: New York, 2003.

(61) Wilk, G. D.; Wallace, R. M.; Anthony, J. M. High-k Gate Dielectrics: Current Status and Materials Properties Consideration. *J. Appl. Phys.* **2001**, *89*, 5243–5275.

(62) Robertson, J. Electronic Structure and Band Offsets of High-Dielectric-Constant Gate Oxides. *MRS Bull.* 2002, 27, 217–221.

(63) Liu, X.; Wang, C.; Cai, B.; Xiao, X.; Guo, S.; Fan, Z.; Li, J.; Duan, X.; Liao, L. Rational Design of Amorphous Indium Zinc Oxide/ Carbon Nanotube Hybrid Film for Unique Performance Transistors. *Nano Lett.* **2012**, *12*, 3596–3601.

(64) Fortunato, E.; Pimentel, A.; Pereira, L.; Goncalves, A.; Lavareda, G.; Aguas, H.; Ferreira, H.; Carvalho, C. N.; Martins, R. High Field-Effect Mobility Zinc Oxide Thin Film Transistors Produced at Room Temperature. *J. Non-Cryst. Solids* **2004**, *338*, 806–809.

(65) Wang, L.; Yoon, M.-H.; Lu, G.; Yang, Y.; Facchetti, A.; Marks, T. J. High-Performance Transparent Inorganic-Organic Hybrid Thin-Film n-Type Transistors. *Nat. Mater.* **2006**, *5*, 893–900.

(66) Hsu, H.; Chang, C.; Cheng, C. A Flexible IGZO Thin-Film Transistor with Stacked  $TiO_2$ -based Dielectrics Fabricated at Room Temperature. *IEEE Electron Device Lett.* **2013**, *34*, 768–770.